八路抢答器课程设计报告

好久没更新过博客了,之前一段时间及比较忙,快要期末了,考试要准备,课程设计要做,中间还水了个自动打卡的脚本,闲下来的时间比较少(可能是打游戏去了),就一直没更新吧,上一次更新是两三周之前,虽然不存在什么有人催更的问题(滑稽),但是自己心里还是不舒服,于是就来水一篇博客。

1、 基本功能

- 抢答器系统提供八路抢答,分别代表八支队伍,分别用按钮S1-S8表示,最先按下按钮的队伍对应的LED灯会亮起来,其他队再按下按钮无效。

- 当按下开始抢答按钮(reset)之后计时模块开始计时30S,扬声器会发出短暂报警,LED灯亮,若30秒之内有队伍按下抢答按钮,则计时模块停止计时,同时扬声器短暂报警;若30S内没有队伍按下抢答按钮,到了30S时计时停止,扬声器短暂报警,且LED灯熄灭。

- 抢答器系统设有清除按钮/开始按钮(reset),第一次按下之后,代表抢答的LED灯亮,计时器开始计时,再次按下,所有的LED灯熄灭,计时器归零,系统回到初始状态。

2、方案设计

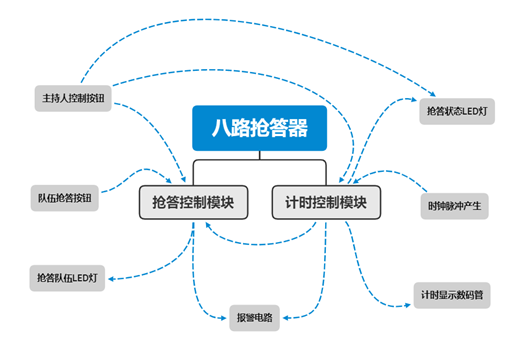

电路分为两个主要的模块——抢答模块和计时模块,报警电路穿插在这两个模块之间,配合两个电路的特点,能够达到报警的效果。

具体结构框图如图1所示:

3、单元电路设计

3.1抢答模块的设计

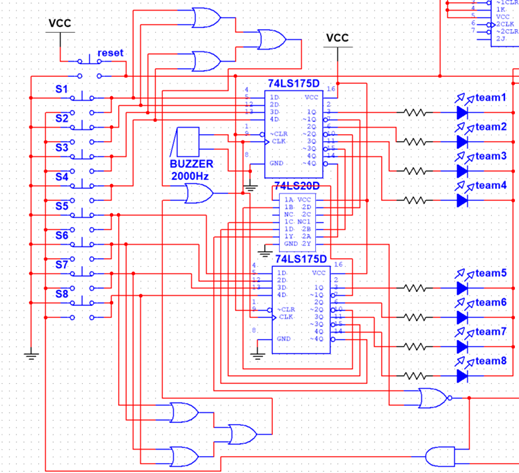

电路仿真图如图2所示。该部分电路主要由74LS175和74LS20芯片构成。该电路主要功能是分辨出最先按下按钮的队伍,并将其锁定,其他队伍再按下按钮无效,同时对应队伍的LED灯亮起。

该电路主要原理是将D触发器输出的结果 经过两个四与非门,反馈给队伍抢答按钮的输入电平。当抢答还没开始的时候,D触发器输出Q都是低电平, 都为高电平,经过与非门之后就是输出为低电平,再将两个与非门或非,结果就为高电平,此时任何一个队伍按下按钮都是有效的。

当有一个队伍已经抢答成功,那么八个D触发器的输出经过两个四输入与非门之后,有一个与非的结果为高电平,再将两者或非,结果就为低电平,此时再有队伍按下抢答按钮就无效,LED灯的亮灭不会发生改变。

D触发器的时钟输入是由八个按钮的电平相或得到,只要有一个队伍在抢答有效的时间内按下按钮,并且在此之前没有其他队伍按下抢答按钮,就会产生一个上升沿;若已有队伍抢答成功,再有队伍按下按钮,电平不会发生变化,时钟不会检测到上升沿。

清零效果的实现主要是利用D触发器的 ~CLR端,清零按钮默认是高电平状态,当按下之后会出现一个低电平的信号,输送给 ~CLR端,达到清零效果。

抢答部分的报警电路是有一个蜂鸣器构成,高电平引脚接的是74LS175的时钟端口,第一个队伍按下按钮之后时钟端会产生一个高电平信号,蜂鸣器得到这个高电平信号之后会,发出短暂的响声,提示已有队伍抢答成功。

3.2计时模块的设计

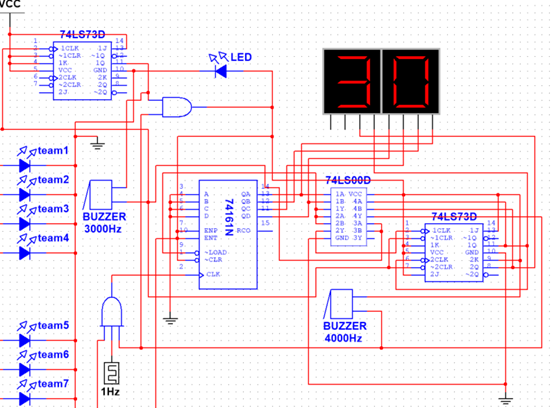

电路仿真图如图3所示。计时模块主要有74LS73、74161和74LS00芯片构成。计时模块的个位数字0-9是74161芯片来控制的,使用反馈清零法,使其在0-9之间循环;十位的数字0-3是由74LS73芯片来控制的,它的时钟信号是74161的置数信号,每当74161需要置数,74LS73就会收到一个时钟脉冲,十位的计数就加一,74161的置数的信号也相当于进位信号。

计时模块的“开关”主要是用74LS73芯片中的JK触发器构成的一个T触发器来实现的,JK触发器的时钟信号是由前面的清零按钮控制,按下清零按钮之后会产生一个下降沿,触发器的输出发生翻转,也就模拟了开关状态的改变。当计时器十位数字为3时,也就是30秒的计时时间到了,74LS73这时Q1和Q2都为高电平,将其接到74LS00的与非门上面,与非的结果为0。再将这个与非的结果和上面JK触发器输出的电平相与得到计时模块的总开关,只要这两者有一个为低电平,总开关就是断开的,计时模块停止工作。比如:当计时器到了30秒的时候74LS73输出Q1和Q2与非的结果为0,此时,计时模块停止工作,数码管显示停留在30秒的时候。计时模块有一个LED指示灯,当“开关”接通时,指示灯亮,当计时到达30秒或者还未开始抢答时,指示灯熄灭。

计时的时钟脉冲是由前面抢答模块的D触发器输出四个四个相与非,再将两个与非的结果或非和74LS73的Q1、Q2或非的结果以及一个1HZ的方波信号三个信号相与的结果,只要有一个条件不满足,计数器就会停止计数。比如:已有人抢答成功,那么第一个条件不满足,计时器停止计数;计时器计时到了30秒,那么第二个条件不满足,计数器停止计数。

计时模块的报警电路有两部分,一个是计时时间到了30秒,蜂鸣器报警,另一个是抢答开始,蜂鸣器发出报警。第一部分蜂鸣器的高电平端口接到计时模块的电源上,低电平端口接到74LS73输出结果相与非后的端口,计时到了30秒时,74LS73输出结果相与非后的结果为0,高低电平端口有电位差,蜂鸣器发出报警声,同时计时模块的“开关”会断开,所以蜂鸣器的高电平端口也会变为低电平,所以蜂鸣器只会短暂报警。第二部分蜂鸣器的高电平端口接到计时模块的JK触发器的输出端,低电平端口接清零按钮的输出。初始状况蜂鸣器高低电平的电位差为-5V,在按下开始抢答按钮的一瞬间,点位差变成5V蜂鸣器会发出短暂报警声。

4、主要元器件的选择

此八路抢答系统主要由两块74LS175、两块74LS73一块74LS20、一块74LS00、一块74161芯片以及若干非门和与门组成。

所有元器件列表:

| 器件名称 | 数量 |

|---|---|

| 74LS175(D触发器) | 2片 |

| 74LS73(JK触发器) | 2片 |

| 74LS20(四输入与非门) | 1片 |

| 74LS00(二输入与非门) | 1片 |

| 74161(十六进制计数器) | 1片 |

| LED | 9个 |

| 电阻(470Ω) | 9个 |

| 两输入或门 | 8个 |

| 两输入或非门 | 1个 |

| 三输入与门 | 1个 |

| 两输入与门 | 1个 |

| PB_DPST按钮 | 9个 |

| 蜂鸣器 | 3个 |

| 数码管 | 2个 |

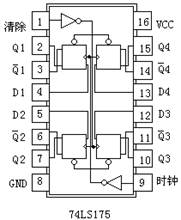

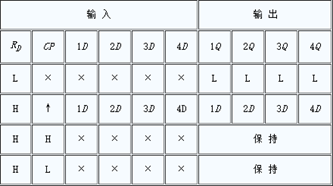

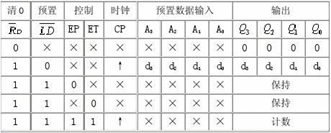

74LS175引脚和逻辑功能表:

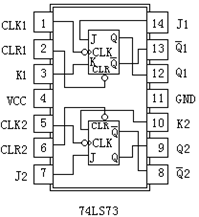

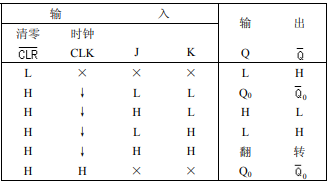

74LS73引脚和逻辑图:

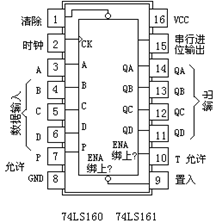

74161引脚和逻辑图:

5、调试结果及分析

5.1调试中存在的问题

1.多个队伍同时按下抢答按钮会显示都抢答成功

造成这一结果的原因,一方面可能是仿真电路的时间步长和实际的时间步长不一致,仿真需要实时的计,算运行的比实际电路要慢很多,就造成了第一个按下的信号还没反馈回去,第二个按下按钮队伍的信号也一起发出来了,最后就出现多个队伍对应的LED亮起;另一方面可能是反馈回给按钮的信号延迟太高,比第一个按下按钮的队伍和第二个按下按钮的队伍的时间差还要长,也是导致第一次按下按钮信号没反馈回去,第二次的信号就发出去了。这种情况就是电路设计的问题了,但是受条件限制,无法搭建实际的电路,只能用仿真调试,具体的原因也无法进一步探究。

2.蜂鸣器不响(只能响一个)

在Multisim仿真里面,用示波器测了蜂鸣器两个端口的电位波形,蜂鸣器两个端口有正向的电位差但是蜂鸣器不会响。经过多次的调试发现需要把蜂鸣器单独拿出来并给它一个正向的电位差,再将其接到实际电路中,这样蜂鸣器就可以响了,但是三个蜂鸣器都经过这样的操作之后,只有最后一个能响。造成这种现象的原因应该是Multisim仿真软件的问题,示波器测得的信号没有问题,不能搭建实际的电路也无法进一步验证。

6、心得体会

经过这次八路抢答器的课程设计,我收获颇多。一是加深了计数器、触发器、编码器、译码器的理解,熟悉的掌握了计数器、D触发器和JK触发器的使用,能将用所学的理论知识实际运用起来。二是明白了,自己想象的、构思的和实际做起来是有一定的差异的,刚开始选这个题目的时候就觉得这个题不难,第一天构思的时候也觉得还好,但是在Multisim搭建电路的时候出现了很多意料之外的问题,有的可能是软件的问题,有的就确实是自己搭建的电路有问题,用到的芯片多了结构复杂起来了,一个地方不小心接错了一根线就会导致整个电路出现问题。还有一点体会就是自己之前画的仿真电路,过一段时间可能就不记得为什么要那么画了,然后又要自己重新推导一遍。

在这次的课程设计中也发现了自己的许多问题,许多还要提高的部分。第一个是对很多元器件、芯片不熟悉,每次使用都要找逻辑功能表,很不方便。另一点是自己设计逻辑电路图的布局和走线还有待加强,这次课程设计的题目涉及到的模块和功能相对较多,各种元器件的布局以及走线就显得很重要了。

总之,经过这次的课程设计,发现了自己存在的许多问题,也有很多的收获,希望在之后的学习中可以进一步提高。